Electric vehicle (EV) battery voltage ratings are trending upward from 400V to 800V, while those of large energy storage systems (ESS) are increasing from 600V-900V toward 1500V. As test engineers evaluate hardware-in-the-loop (HIL) requirements for the battery management systems (BMS) that manage these batteries, they face a trade-off between simulated cell channel count and simulation accuracy. When not enough cell channels are available, the system often needs to be downscaled via the DUT's special test firmware. However, this approach omits the complexity of real systems comprising hundreds of cells, making it difficult to accurately simulate multi-point faults or scenarios where different failures interact. On the other hand, using battery cell simulators with all the required channels is both costly and space intensive.

High-voltage lithium-ion battery packs for EVs and large ESS typically use a distributed BMS architecture comprising Battery Control Units (BCU) and Battery Management Units (BMU). BMUs are responsible for monitoring data such as cell voltage and temperature, and performing cell balancing. BCUs then use this information to manage the battery pack, safety, and external communication. In high-voltage environments, ISO-SPI technology has become the mainstream choice for internal communication due to its high voltage isolation and low cost.

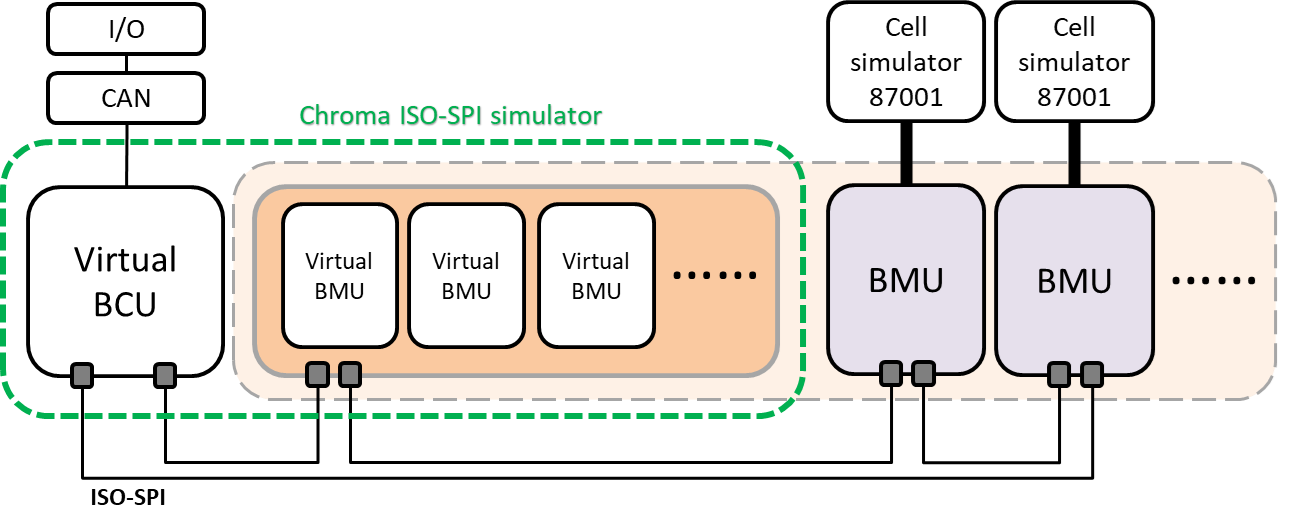

By using ISO-SPI simulation technology to replicate interactions between BCU and BMU, the BCU board can be made to recognize virtual BMUs as parts of a complete system. The technology can also simulate the BCU to test BMU modules independently. In this way, a complete test platform can be built without needing high-channel-count cell simulators and all physical devices under test (DUTs).

▲A hybrid test system combining Chroma's ISO-SPI simulator with multiple virtual BMUs and cell simulators

▲Chroma's ISO-SPI simulator can simulate a BCU for independent testing of individual BMUs

This technology needs to meet two key requirements:

- High Speed: Taking for example the NXP MC33771B and MC33664 IC combination commonly used in BMS applications, with ISO-SPI data rates reaching up to 2Mbps, the simulation system needs to be capable of responding quickly and maintaining stable communication.

- High Compatibility: Different IC brands vary significantly in data formats and control procedures. The simulator needs to have the ability to update its hardware and software for broad compatibility.

Chroma's ISO-SPI simulation technology is built on an FPGA architecture. Through firmware upgrades, it has the flexibility to support various front-end processing and communication ICs used in BMS, meeting both speed and compatibility requirements.

The Chroma 8630 BMS Power HIL Testbed incorporates this technology to form a complete BMS test platform by combining cell simulators with virtual DUTs. This supports dynamic real and virtual scenarios, fault injection, and model integration testing, significantly reducing cost of test and making it a highly efficient tool for battery development and testing.

For more information, please visit the Chroma website and leave your requirements and contact information. We are happy to be of service.

| BMS Power HIL Testbed Model 8630 |